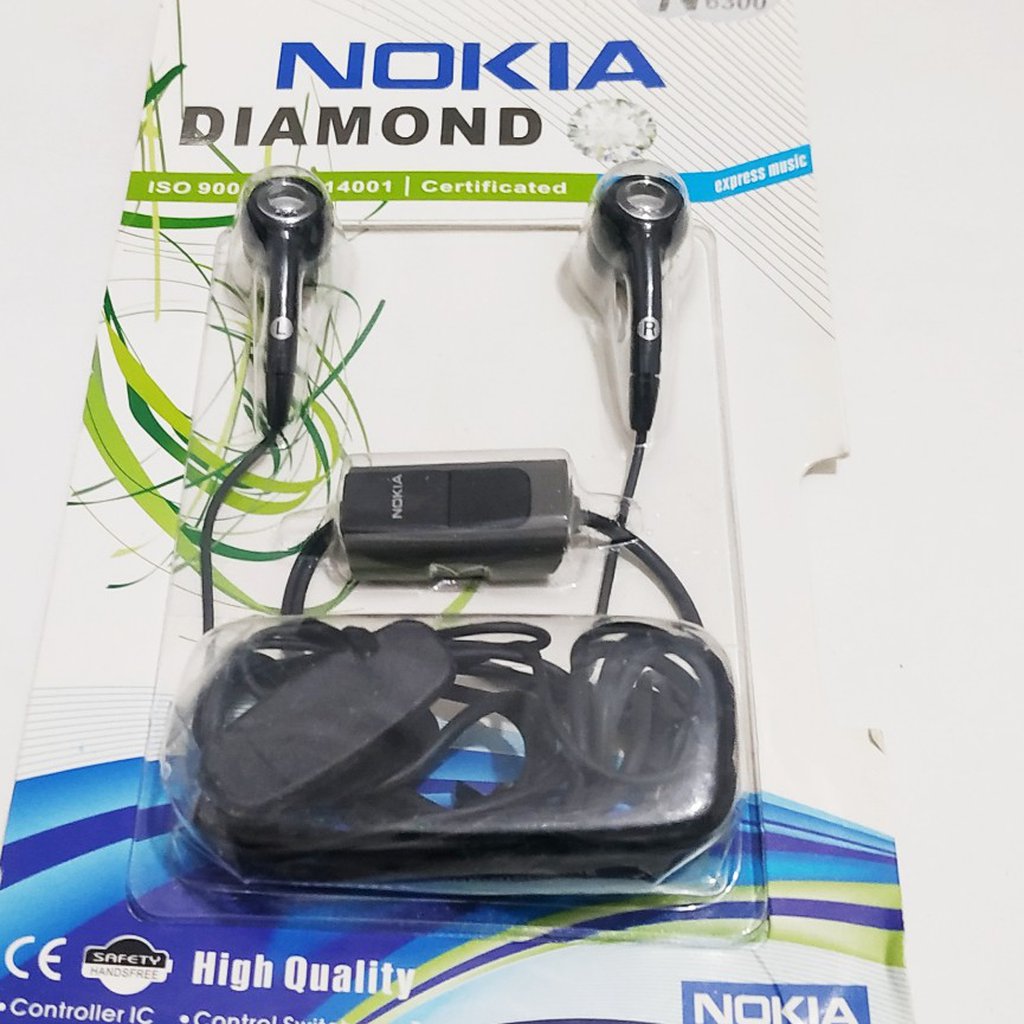

2 adet yeni kulak hoparlör alıcı kulaklık değiştirme için Nokia 2017 Nokia 3310 (2017) TA-1030 Lumia 530 1020 en kaliteli - AliExpress

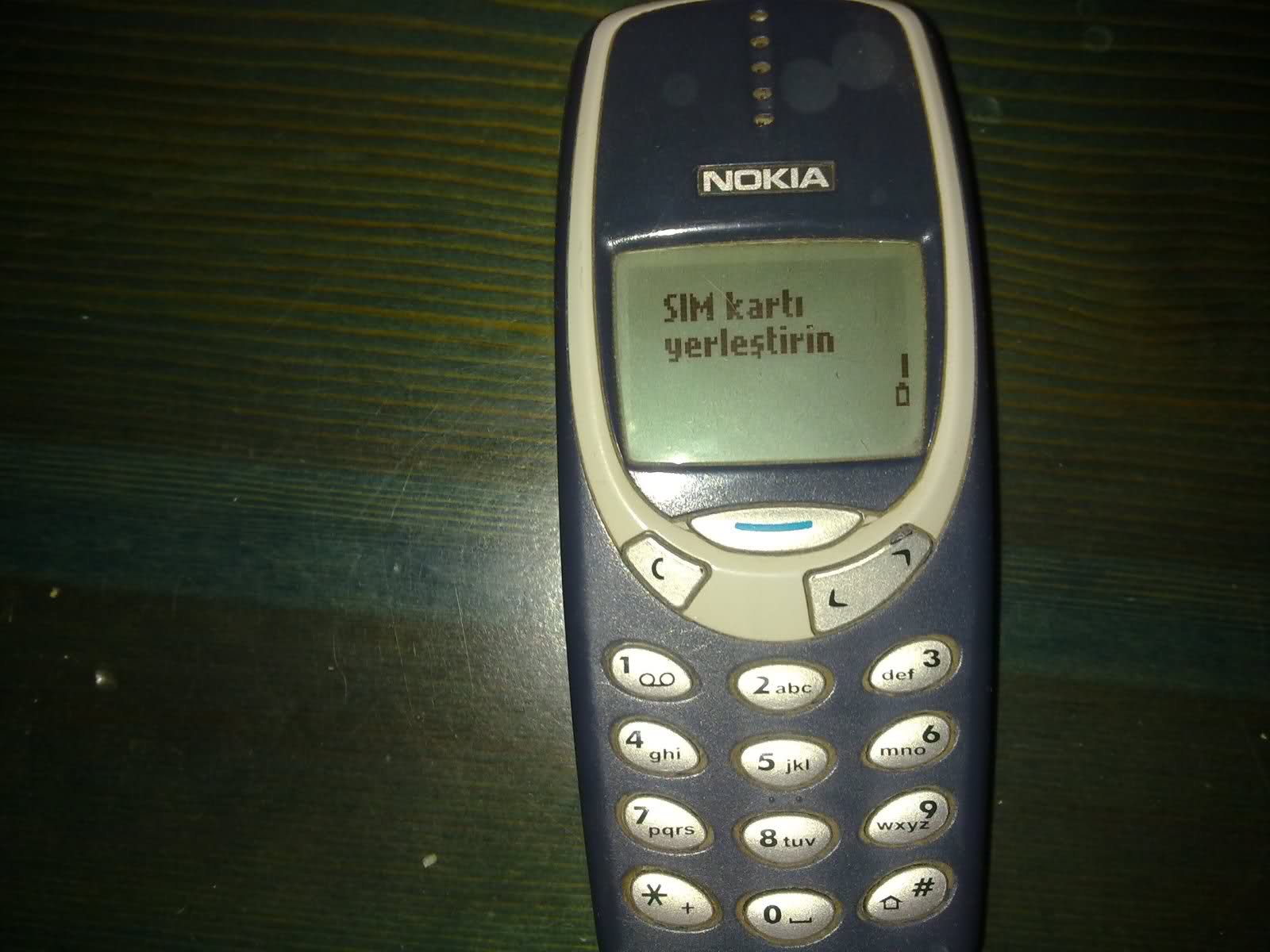

90% yeni, Nokia 3310 telefon anakart LCD ekran için kullanılan titreşim hoparlör kulaklık şarj portu vida aracı parçaları değiştirin - AliExpress

Cep Telefonları BM200 Mini Telefon SIM Kilitli MobilePhone GSM 2G Kablosuz Kulaklık Bluetooth Çevirici Kulaklık Yi TL945.07 | DHgate