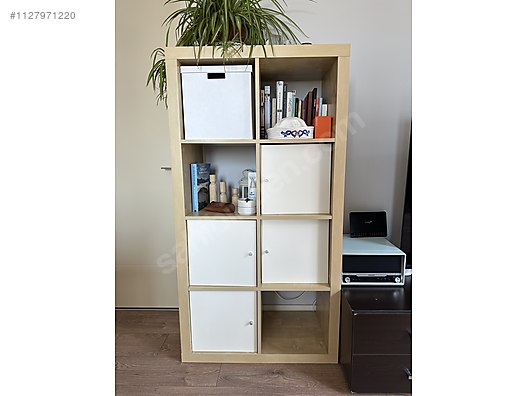

İlk Günkü Gibi Temiz İkea Kitaplık - Ikea Fiyatları ve Diğer Mobilyalar sahibinden.com'da - 1127971220

İkea kitaplık - Ikea Kitaplık Fiyatları ve Çocuk & Genç Odası Mobilyaları sahibinden.com'da - 1024701834

IKEA Bottna Sergi Rafı 36x32cm Bej (billy Kitaplıklar Için Kullanılır) Bd002 Fiyatı, Yorumları - Trendyol

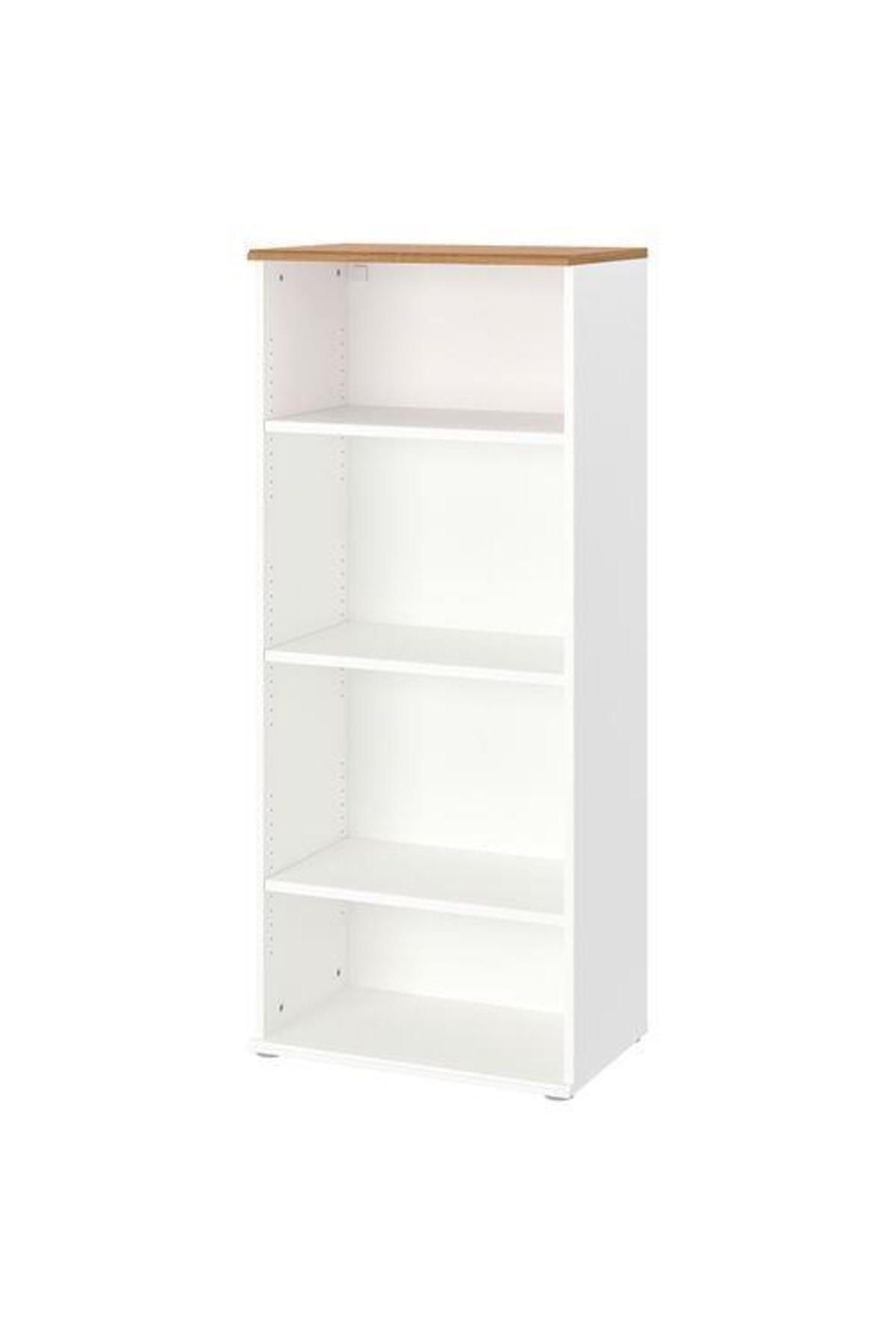

IKEA Açık Kitaplık Raf Ünitesi Beyaz Renk Meridyendukkan 60x140 Cm Ev Dekorasyonu Fiyatı, Yorumları - Trendyol

İkea Ahşap Raf/ Kitaplık - Ikea Kitaplık Fiyatları ve Çocuk & Genç Odası Mobilyaları sahibinden.com'da - 1144061254